## UML-Based Specification of State-Oriented Real-Time Properties

Dissertation

A thesis submitted to the Faculty of Computer Science, Mathematics and Electrical Engineering of the Universität Paderborn in partial fulfillment of the requirements for the degree of Dr. rer. nat.

by

## Stephan Flake

Paderborn, December 2003

Supervisors:

- 1. Prof. Dr. rer. nat. Franz J. Rammig, Universität Paderborn

- 2. Prof. Dr. rer. nat. Gregor Engels, Universität Paderborn

- 3. Prof. Dr. rer. nat. Martin Gogolla, Universität Bremen

Date of public examination: December 19, 2003

**Dedicated to my family**

## Abstract

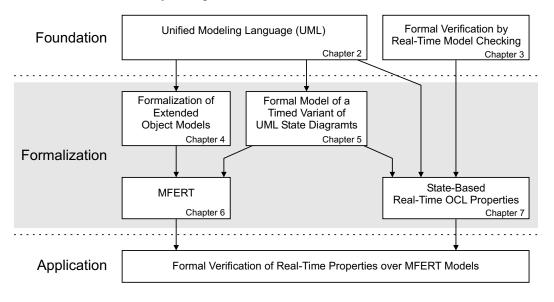

In recent years, the Unified Modeling Language (UML) has received significant attention by software designers to model object-oriented software systems. Complementary to UML diagrams, modelers can make use of the textual Object Constraint Language (OCL) to specify additional constraints for their models. OCL is particularly used to formulate constraints over a given UML model in form of class invariants and operation pre- and postconditions. However, the semantics of OCL is still incomplete, even in the latest OCL 2.0 proposal that has recently been adopted by the Object Management Group. While it is allowed to make use of states from State Diagrams in OCL expressions to reason about their activations, there is currently no corresponding semantics defined in the adopted OCL 2.0 specification. As a first goal, this thesis closes that gap and provides a formal notion of state configurations over UML State Diagrams that is integrated into the formal semantics of the adopted OCL 2.0 specification.

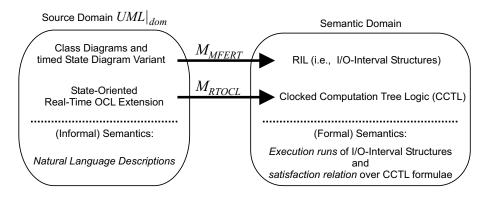

The second major goal of this thesis is to extend OCL to support specification and analysis of temporal state-oriented constraints for UML models of time-critical software-controlled systems. In order to demonstrate the applicability of this extension, the thesis focuses on early stages of the software development process and applies time-bounded state-oriented OCL constraints to specify requirements in the domain of modeling time-constrained manufacturing systems. For the structural modeling of manufacturing systems a restricted version of UML Class Diagrams is employed, and for the behavioral modeling a timed UML State Diagram variant with a corresponding time-related semantics is presented.

In addition, this thesis also provides a semantics for both the regarded kind of UML models and the time-bounded state-oriented OCL extension by mappings to formal target languages, i.e., time-annotated state-transition systems and temporal logics. This allows to perform automated formal analysis with existing verification tools. The motivation behind the mapping is the idea to abstract from the rather cryptical input languages of verification tools, in particular the temporal logics used in the formal verification technique called model checking.

# Contents

| 1 | Intro                        | Introduction 5                                         |   |  |  |  |  |

|---|------------------------------|--------------------------------------------------------|---|--|--|--|--|

|   | 1.1                          | Research Goals and Contributions                       |   |  |  |  |  |

|   | 1.2                          | Example: Manufacturing Case Study                      | 0 |  |  |  |  |

|   | 1.3                          | Outline                                                | 3 |  |  |  |  |

| 2 | Unified Modeling Language 15 |                                                        |   |  |  |  |  |

|   | 2.1                          | UML Language Definition                                | 5 |  |  |  |  |

|   | 2.2                          | Survey of UML Diagrams                                 | 8 |  |  |  |  |

|   | 2.3                          | Details of Selected Parts of UML                       | 1 |  |  |  |  |

|   |                              | 2.3.1 UML Class Diagrams                               | 1 |  |  |  |  |

|   |                              | 2.3.2 UML State Diagrams                               | 4 |  |  |  |  |

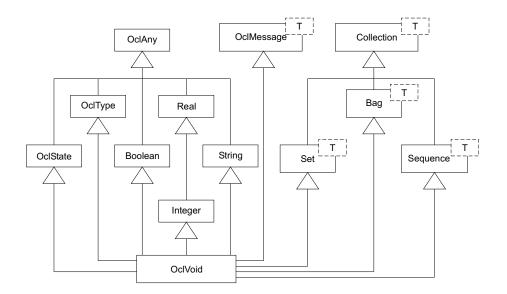

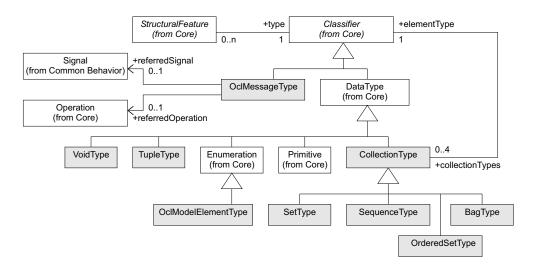

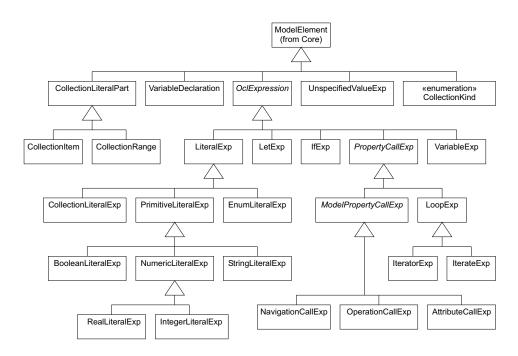

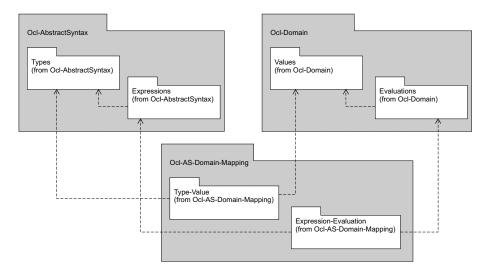

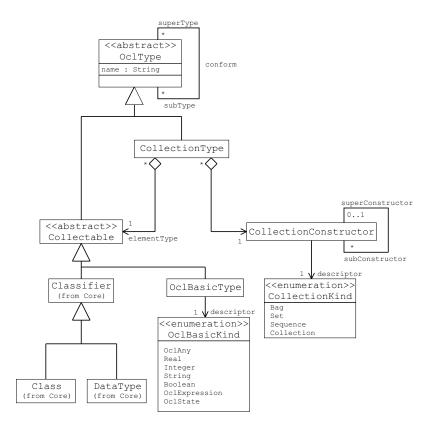

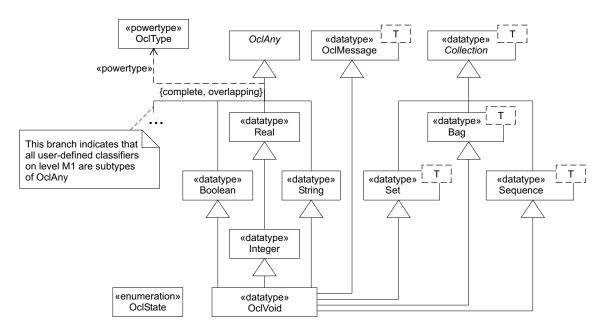

|   |                              | 2.3.3 Object Constraint Language                       | 9 |  |  |  |  |

|   |                              | 2.3.4 UML Extension Mechanisms                         | 7 |  |  |  |  |

|   | 2.4                          | UML and Time                                           | 8 |  |  |  |  |

|   |                              | 2.4.1 Time and Timing Constraints in Standard UML      | 9 |  |  |  |  |

|   |                              | 2.4.2 Modeling Real-Time System Architectures with UML | 0 |  |  |  |  |

|   |                              | 2.4.3 Time-Annotated State Diagrams                    | 1 |  |  |  |  |

|   | 2.5                          | Contributions of the Chapter                           | 4 |  |  |  |  |

| 3 | Forr                         | nal Verification 5.                                    | 5 |  |  |  |  |

|   | 3.1                          | Automata-Based Modeling Approaches                     | 6 |  |  |  |  |

|   | 3.2                          | Formal Specification                                   | 8 |  |  |  |  |

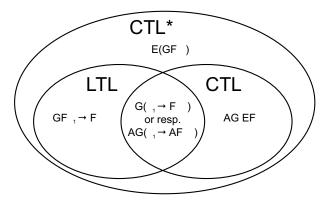

|   |                              | 3.2.1 Temporal Logics                                  | 8 |  |  |  |  |

|   |                              | 3.2.2 Property Specification Patterns                  | 2 |  |  |  |  |

|   | 3.3                          | Symbolic Model Checking                                | 6 |  |  |  |  |

|   | 3.4                          | Real-Time Model Checking                               |   |  |  |  |  |

|   | 3.5                          | Selection of a Real-Time Model Checking Tool           |   |  |  |  |  |

|   | 3.6 RAVEN                    |                                                        |   |  |  |  |  |

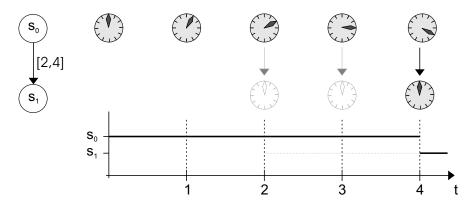

|   |                              | 3.6.1 Interval Structures                              | 2 |  |  |  |  |

|   |                              | 3.6.2 Clocked Computation Tree Logic                   | 7 |  |  |  |  |

|   |                              | 3.6.3 RAVEN Input Language (RIL)                       | 9 |  |  |  |  |

|   |                              | 3.6.4 Graphical User Interface                         | 2 |  |  |  |  |

|   | 3.7                          | Contributions of the Chapter                           | 3 |  |  |  |  |

| 4 | Exte | Extended Object Model 8 |                                                       |     |  |  |  |  |  |

|---|------|-------------------------|-------------------------------------------------------|-----|--|--|--|--|--|

|   | 4.1  | Syntax                  |                                                       | 86  |  |  |  |  |  |

|   |      | 4.1.1                   | Types                                                 | 87  |  |  |  |  |  |

|   |      | 4.1.2                   | Classes and their Characteristics                     | 88  |  |  |  |  |  |

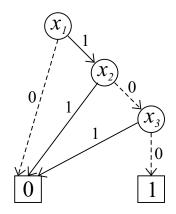

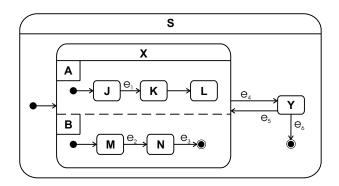

|   |      | 4.1.3                   | Abstract Syntax of State Diagrams                     | 91  |  |  |  |  |  |

|   |      | 4.1.4                   | Associations                                          | 96  |  |  |  |  |  |

|   |      | 4.1.5                   | Generalization                                        | 98  |  |  |  |  |  |

|   | 4.2  | Seman                   | tics                                                  | 100 |  |  |  |  |  |

|   |      | 4.2.1                   | Objects                                               | 101 |  |  |  |  |  |

|   |      | 4.2.2                   | A Note about State Diagram Inheritance                | 101 |  |  |  |  |  |

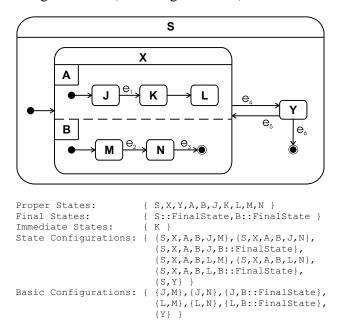

|   |      | 4.2.3                   | State Configurations                                  | 102 |  |  |  |  |  |

|   |      | 4.2.4                   | Links                                                 | 104 |  |  |  |  |  |

|   |      | 4.2.5                   | System State                                          | 105 |  |  |  |  |  |

|   |      | 4.2.6                   | Semantics of Operation oclInState(statename:OclState) | 107 |  |  |  |  |  |

|   |      | 4.2.7                   | Traces                                                | 108 |  |  |  |  |  |

|   | 4.3  | Discus                  | sion                                                  | 112 |  |  |  |  |  |

|   | 4.4  | Contril                 | butions of the Chapter                                | 113 |  |  |  |  |  |

| 5 | АТ   | imed UN                 | ML State Diagram Variant                              | 115 |  |  |  |  |  |

| 5 | 5.1  |                         | tical Restrictions                                    |     |  |  |  |  |  |

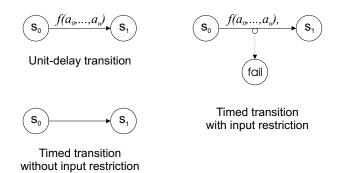

|   | 5.2  | •                       |                                                       |     |  |  |  |  |  |

|   | 5.3  |                         | tics                                                  |     |  |  |  |  |  |

|   | 5.4  |                         | ation to I/O-Interval Structures                      |     |  |  |  |  |  |

|   | 5.1  | 5.4.1                   | Generating I/O-Interval Structures                    |     |  |  |  |  |  |

|   |      | 5.4.2                   | Transition Mapping                                    |     |  |  |  |  |  |

|   | 5.5  |                         | butions of the Chapter                                |     |  |  |  |  |  |

|   | 5.5  |                         |                                                       |     |  |  |  |  |  |

| 6 | MF   | MFERT 145               |                                                       |     |  |  |  |  |  |

|   | 6.1  | MFER                    | T Graphs                                              | 147 |  |  |  |  |  |

|   | 6.2  | Formal                  | I MFERT Model                                         | 147 |  |  |  |  |  |

|   | 6.3  | Dynam                   | nic Semantics of MFERT                                | 150 |  |  |  |  |  |

|   |      | 6.3.1                   | Production Process Nodes                              | 150 |  |  |  |  |  |

|   |      | 6.3.2                   | Production Element Nodes                              | 152 |  |  |  |  |  |

|   |      | 6.3.3                   | Message Passing                                       | 152 |  |  |  |  |  |

|   |      | 6.3.4                   | Conflict Resolution in PENs                           | 153 |  |  |  |  |  |

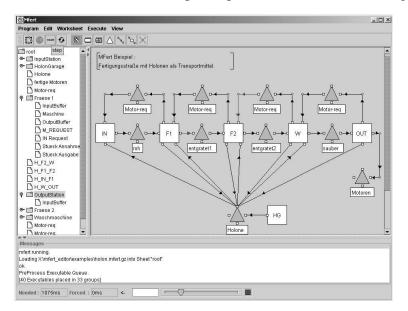

|   |      | 6.3.5                   | Simulation Implementation                             | 153 |  |  |  |  |  |

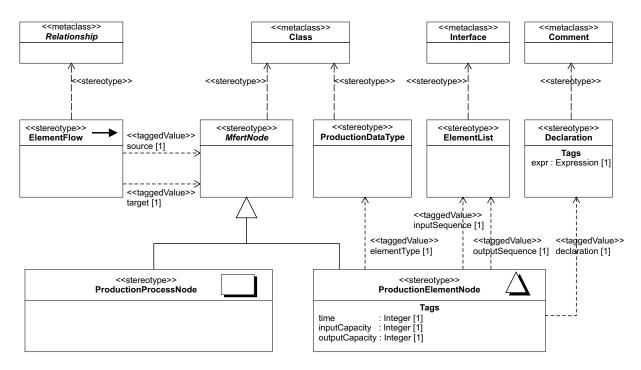

|   | 6.4  | A UM                    | L Profile for MFERT                                   | 154 |  |  |  |  |  |

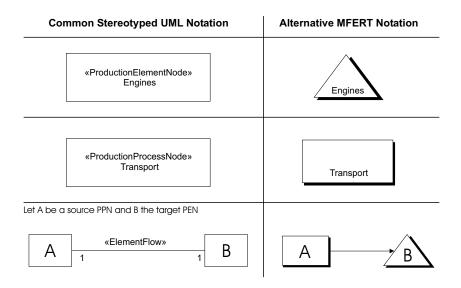

|   |      | 6.4.1                   | MFERT Graphical Notation in Class Diagrams            | 155 |  |  |  |  |  |

|   |      | 6.4.2                   | Validation Constraints                                | 156 |  |  |  |  |  |

|   |      | 6.4.3                   | Mapping to the Formal MFERT Model                     | 157 |  |  |  |  |  |

|   | 6.5  | Contril                 | butions of the Chapter                                | 158 |  |  |  |  |  |

#### CONTENTS

| Real-Time Properties with OCL           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |  |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|

| 7.1                                     | UML Profile for Real-Time Constraints with OCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 162                                                      |  |  |

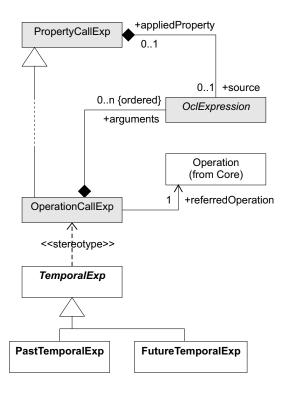

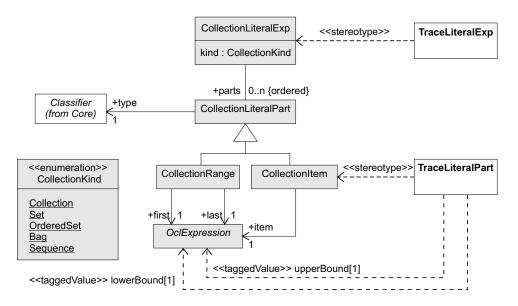

|                                         | 7.1.1 OCL Metamodel Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 163                                                      |  |  |

|                                         | 7.1.2 Concrete Syntax Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 165                                                      |  |  |

|                                         | 7.1.3 Standard Library Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 169                                                      |  |  |

|                                         | 7.1.4 Semantics of Temporal Expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 171                                                      |  |  |

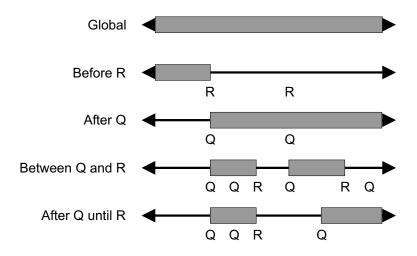

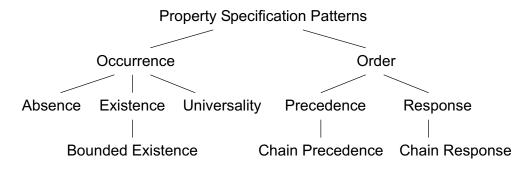

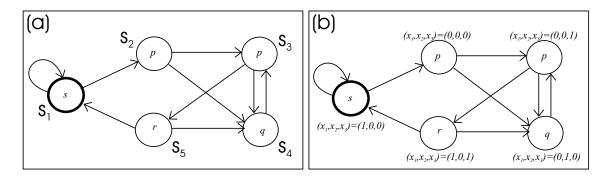

| 7.2                                     | Expressing Specification Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 172                                                      |  |  |

| 7.3                                     | Mapping to the Temporal Logics CCTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 175                                                      |  |  |

| 7.4                                     | Temporal OCL Queries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 177                                                      |  |  |

| 7.5                                     | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 178                                                      |  |  |

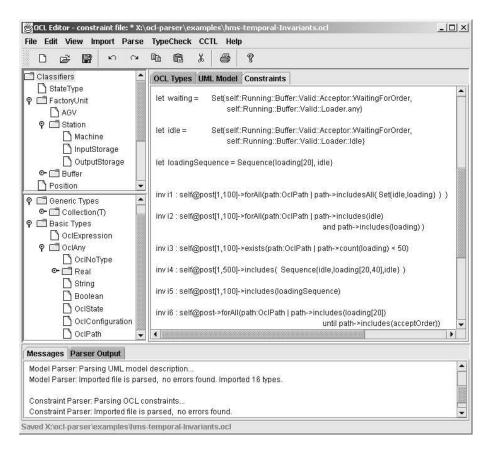

| 7.6                                     | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 180                                                      |  |  |

| 7.7                                     | Contributions of the Chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 180                                                      |  |  |

| Manufacturing Case Study                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |  |  |

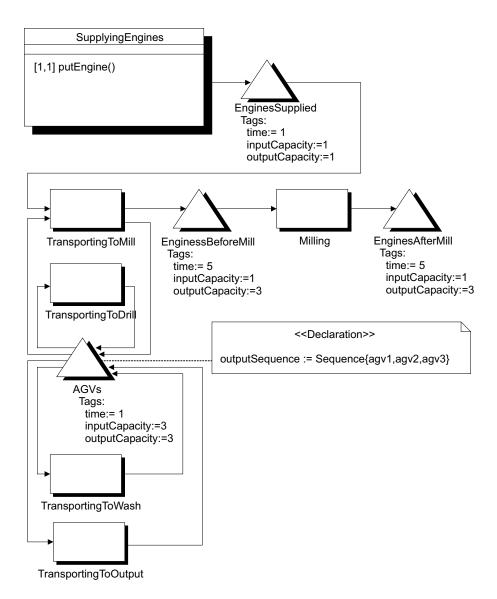

| 8.1                                     | The MFERT Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 184                                                      |  |  |

| 8.2                                     | Real-Time OCL Constraints and CCTL Formulae                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 191                                                      |  |  |

| Conclusion                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |  |  |

| 9.1                                     | Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 197                                                      |  |  |

| eratu                                   | ire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 199                                                      |  |  |

| Tim                                     | ed Finite State Machines for PPNs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 211                                                      |  |  |

| A.1                                     | Help Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 211                                                      |  |  |

| A.2                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |  |  |

| A.3                                     | Consumption and Production Actions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 213                                                      |  |  |

| A.4                                     | Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 213                                                      |  |  |

| A.5                                     | Mapping to I/O-Interval Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 213                                                      |  |  |

| OCI                                     | 2 Metalevel Operations for Classifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 215                                                      |  |  |

| Structural Constraints for MFERT Models |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |  |  |

| C.1                                     | ProductionDataType                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 217                                                      |  |  |

| C.2                                     | ElementList                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 218                                                      |  |  |

| C.3                                     | MFERTNode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 219                                                      |  |  |

| C.4                                     | ProductionProcessNode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 220                                                      |  |  |

| C.5                                     | ProductionElementNode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 220                                                      |  |  |

| C.6                                     | ElementFlow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 221                                                      |  |  |

| Prop                                    | perty Specification Patterns with OCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 223                                                      |  |  |

|                                         | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>Man<br>8.1<br>8.2<br>Con<br>9.1<br>Con<br>9.1<br>Con<br>9.1<br>Con<br>9.1<br>Con<br>9.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>0.1<br>Con<br>Con<br>Con<br>Con<br>Con<br>Con<br>Con<br>Con<br>Con<br>Con | 7.1       UML Profile for Real-Time Constraints with OCL |  |  |

### CONTENTS

# Chapter 1 Introduction

I'm writing a book. I have the page numbers down... I just have to fill in the rest. – Steven Wright

Developing software systems is a difficult and error-prone task. Nowadays, software is still in almost all cases developed in a rather pragmatic way. In the software design process, different software development phases are usually identified. Basically, they can be separated into phases like informal requirement gathering, analysis, specification, design, implementation, and testing. These phases are not strictly sequential but rather overlapping, iterative, or carried out in parallel for different parts of the system under development.

While some approaches focus on the implementation of a system already in early phases of development (e.g., eXtreme programming [Bec00]), others try to separate system modeling from the actual task of implementation. Latter approaches mostly use a *platform-independent model* for the complete design of an application. One of the most popular approaches in this context is the *Model-Driven Architecture* (MDA) by the Object Management Group [OMG] that bases upon industrial modeling standards like the Unified Modeling Language (UML), Meta Object Facility (MOF), and XML Metadata Interchange (XMI). From these standards, UML provides means to build object-oriented models of a system under consideration in form of a rich set of standardized graphical diagrams.

**UML.** UML unifies a number of different modeling languages and is still undergoing a development under the control of the OMG consortium. At the time of writing this thesis, the latest official version released by the OMG is UML 1.5, published in March 2003 [OMG03d]. More recently, the OMG adopted a number of proposals to build a new version of UML, i.e., UML 2.0. These proposals are still undergoing a finalization process. In the context of this thesis, the adopted proposal for a new version of the Object Constraint Language [OMG03b] is of particular interest, while the proposals for a UML 2.0 Infrastructure [OMG03e] and a UML 2.0 Superstructure [OMG03f] have less impact on this work.

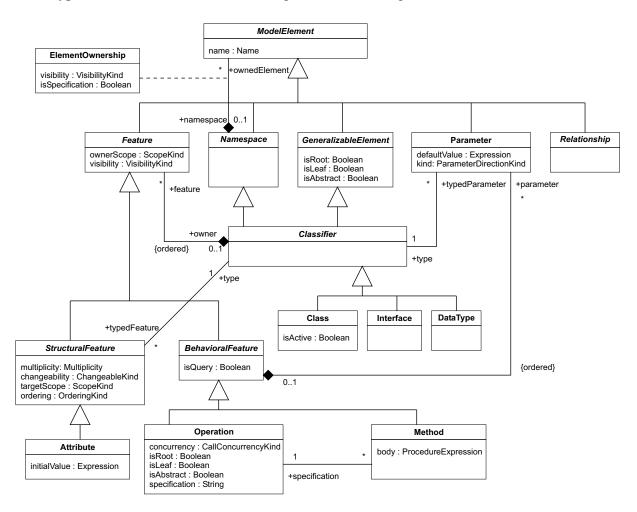

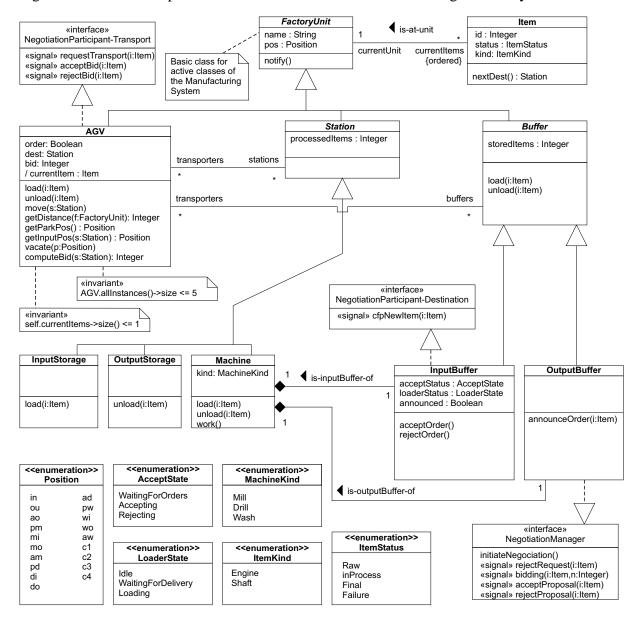

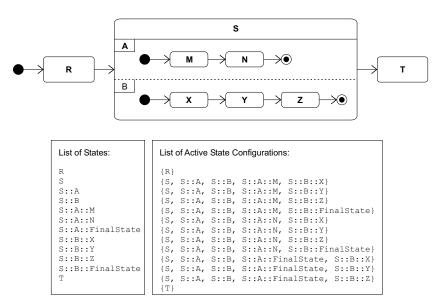

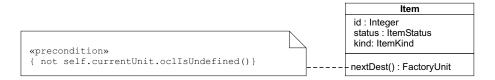

UML defines a number of diagrams to model different aspects of the structure and behavior of software systems. For example, Class Diagrams are used to describe the static structure of a system, while UML State Diagrams model the (reactive) behavior of objects. In addition to the set of diagrams, the textual Object Constraint Language (OCL) is an integral part of the UML to specify restrictions on values of parts of UML models. Basically, OCL constraints are invariants attached to classes or pre- and postconditions of operations. Significant parts of OCL have already been formally defined in [Ric01] in form of a set-theoretic *object model*. That work heavily influenced the formal semantics of the adopted OCL 2.0 specification [OMG03b]. However, the formal semantics of OCL is still incomplete, as it currently lacks an integration of UML State Diagrams, although it is already possible to formulate constraints that refer to the states specified in UML State Diagrams. One aspect of this thesis is to extend the formal semantics of OCL by a formal integration of UML State Diagrams and to provide the formal semantics for state-related OCL operations.

UML has already been applied in different application domains, e.g., to model *time-critical* software-controlled systems such as embedded real-time systems [Dou00]. For time-critical systems, correct time-constrained behavior is an essential requirement to meet, e.g., timing bounds for message delays and progress of system execution. In this context, it is desirable to be able to identify improper behavior w.r.t. these *timing requirements* already in early phases of development. Otherwise, overall goals like meeting project deadlines and adherence to estimated costs may fail due to the need of time-consuming and expensive re-designs at a later stage of development.

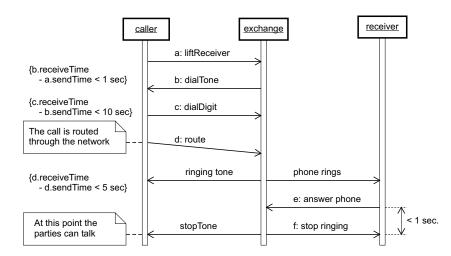

The current version 1.5 of UML as well as the corresponding, recently adopted UML 2.0 proposals provide some basic means to specify timing requirements. In particular, timing annotations can be applied in Sequence Diagrams to specify timing bounds for durations of message transfers and replies to messages sent. However, UML does not have an inherent timing model, as it is designed to be a general modeling language with a focus on software systems, such that these means are not well integrated into the core concepts of UML.

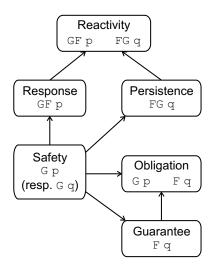

Properties concerning the temporal behavior, such as safety or liveness constraints [Lam77], cannot be expressed with standard UML means. Different approaches have already introduced corresponding extensions, in particular, extensions of UML Sequence Diagrams to enhance time-bounded specifications of communication flow among objects have been published in [DK01, FHD<sup>+</sup>99, KMR02]. In contrast, this thesis introduces a consistent temporal extension of the textual constraint language OCL and focuses on specification of time-bounded state-oriented constraints to reason about the time-critical progress of system execution.

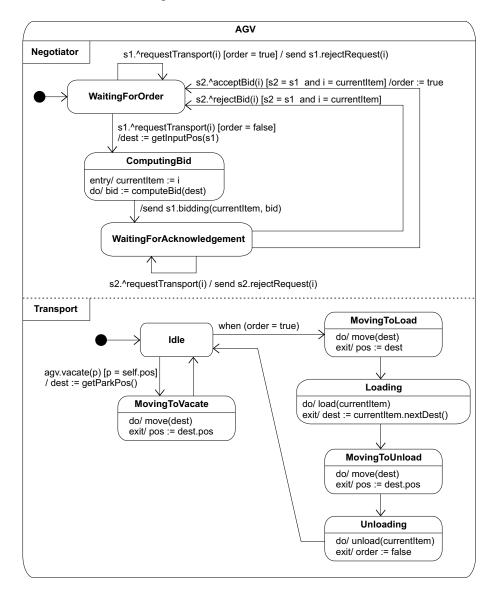

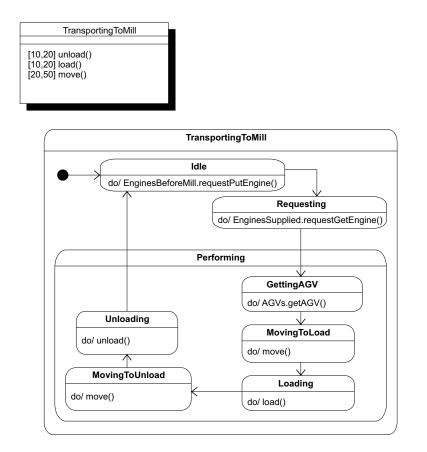

OCL constraints do not make sense without a given model to refer to. In order to have a corresponding timed UML model to refer to, this thesis introduces a timed UML State Diagram variant for behavioral modeling. This State Diagram variant supports a set of UML model elements that have so far not been considered in related work on timed UML State Diagrams (cf. [EW00, DM01, KMR02]). In particular, the presented timed UML State Diagram variant preserves UML model elements like interlevel transitions, synchronous and asynchronous event communication, elapsed time events, and activities that have a notable duration.

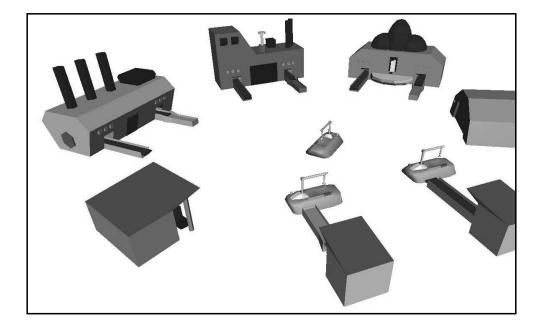

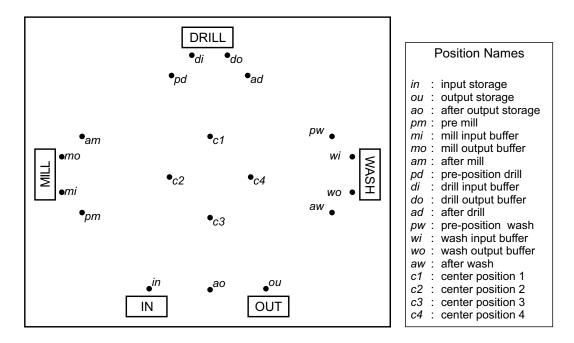

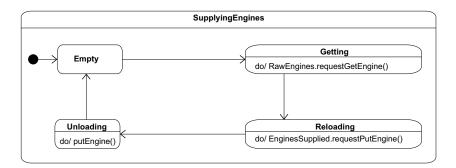

**MFERT.** To validate the applicability of the temporal state-oriented OCL extension, the domain of modeling manufacturing systems is chosen. Manufacturing systems are time-critical

w.r.t. production flow, i.e., production progress is time-bounded and corresponding deadlines have to be met.

This thesis builds upon an existing graphical notation for modeling manufacturing systems, i.e., MFERT.<sup>1</sup> MFERT is a general description scheme for modeling in the domain of manufacturing systems [DW93, Sch96, DW97]. It has been successfully applied in different projects with various industrial partners and is acknowledged by the German science award of logistics. Similar to Petri Nets, the structure of an MFERT model is a bipartite graph of nodes that represent either production processes or storages for production elements. Directed edges between nodes denote the flow of production elements.